CH32V307RCT6

32-bit Interconnectivity RISC-V MCU – CH32V307

Warning: get_headers(): SSL operation failed with code 1. OpenSSL Error messages: error:14090086:SSL routines:ssl3_get_server_certificate:certificate verify failed in /www/wwwroot/default/klayerslocal/wp-content/themes/klayers/single-product.php on line 60

Warning: get_headers(): Failed to enable crypto in /www/wwwroot/default/klayerslocal/wp-content/themes/klayers/single-product.php on line 60

Warning: get_headers(https://static.klayers.net/pdf/2308/CH32V307DS0-Qinheng_KL-229-0004814.pdf): failed to open stream: operation failed in /www/wwwroot/default/klayerslocal/wp-content/themes/klayers/single-product.php on line 60

Warning: Division by zero in /www/wwwroot/default/klayerslocal/wp-content/themes/klayers/functions.php on line 634

Warning: get_headers(): SSL operation failed with code 1. OpenSSL Error messages: error:14090086:SSL routines:ssl3_get_server_certificate:certificate verify failed in /www/wwwroot/default/klayerslocal/wp-content/themes/klayers/single-product.php on line 60

Warning: get_headers(): Failed to enable crypto in /www/wwwroot/default/klayerslocal/wp-content/themes/klayers/single-product.php on line 60

Warning: get_headers(https://static.klayers.net/pdf/2308/CH32FV2x_V3xRM-Qinheng_KL-229-0004814.pdf): failed to open stream: operation failed in /www/wwwroot/default/klayerslocal/wp-content/themes/klayers/single-product.php on line 60

Warning: Division by zero in /www/wwwroot/default/klayerslocal/wp-content/themes/klayers/functions.php on line 634

SKU: KL-229-0004832

Category: Microcontroller Units (MCUs/MPUs/SOCs)

About this item

| Attribute | Value |

|---|---|

| Manufacturer | WCH(Jiangsu Qin Heng) |

| Frequency | 144MHz |

| Flash | 256K |

| SRAM | 64K |

| GPIO | 51 |

| Adv Timer | 4 |

| WDOG | 2 |

| RTC | 1 |

| ADC Unit/CH | 2/16 |

| Touchkey | 16 |

| DAC | 2 |

| OPA | 4 |

| SPI | 3 |

| UART | 8 |

| CAN | 2 |

| USB2.0 FS | OTG |

| USB2.0 HS | H/D built-in PHY |

| Ethernet | 1G MAC+10M PHY |

| SDIO | 1 |

| TRNG | 1 |

| VDD | 2.5V; 3.3V; |

| Package | LQFP64M |

| GP Timer | 4 |

| IIS | 2 |

Overview

The CH32V305/7 is an interconnectivity MCUs based on 32-bit RISC-V core, with hardware stack area and fast interrupt entry. Compared with standard RISC-V, the interrupt response speed is greatly improved. With single-precision float point instruction sets added and stack area extended, the CH32V305/7 features higher performance, the number of UARTs is extended to 8, and the number of motor timers is extended to 4. The CH32V305/7 provides USB2.0 high-speed interface (480Mbps), built-in PHY transceiver and Ethernet MAC upgraded to GbE, and integrates 10M PHY module.

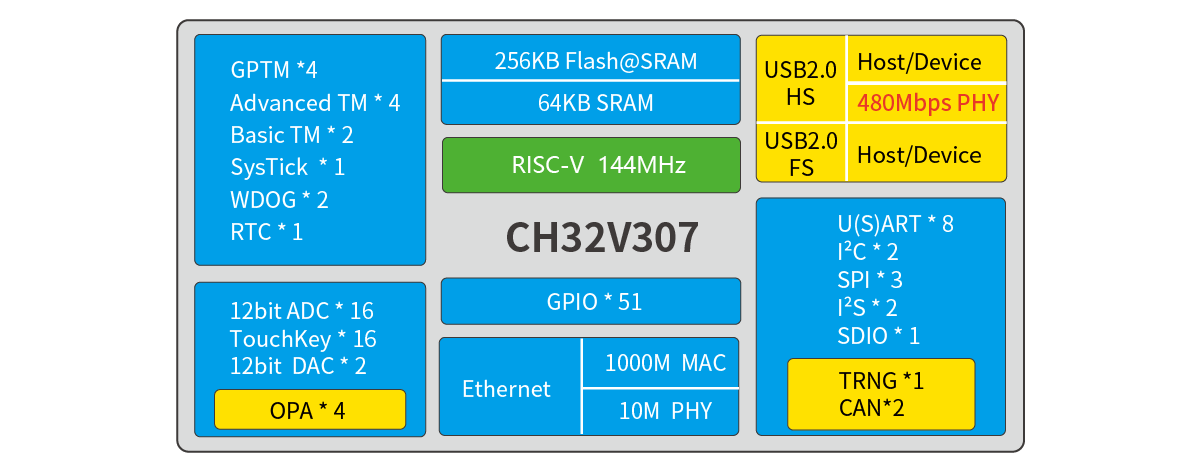

System Block Diagram

Features

- Qingke V4F processor, up to 144MHz system clock frequency.

- Single-cycle multiplication and hardware division. Hardware float point unit (FPU).

- 64KB SRAM, 256KB Flash.

- Supply voltage: 2.5V/3.3V. GPIO unit is supplied independently.

- Low-power modes: sleep/stop/standby.

- Power-on/power-down reset (POR/PDR), programmable voltage detector (PVD).

- 2 general DMA controllers, 18 channels in total.

- 4 amplifiers.

- One true random number generator (TRNG).

- 2 x 12-bit DAC.

- 2-unit 16-channel 12-bit ADC, 16-channel TouchKey.

- 10 timers.

- USB2.0 full-speed OTG interface.

- USB2.0 high-speed host/device interface (built-in 480Mbps PHY).

- 3 USARTs, 5 UARTs.

- 2 CAN interfaces (2.0B active).

- SDIO interface, FSMC interface, DVP.

- 2 IIC interfaces, 3 SPI interfaces, 2 IIS interfaces.

- Gigabit Ethernet controller ETH (built-in 10M PHY).

- 80 I/O ports, can be mapped to 16 external interrupts;

- CRC calculation unit, 96-bit unique ID.

- Serial 2-wire debug interface.

- Packages: LQFP64M, LQFP100.

Product Selection Guide

Send your message to supplier

Buy More, Save More!

Unit Price$2.3854

11688 in stock

How to buy?

- Please enter the quantity you need, then click GET QUOTATION NOW button to add the products to your cart, no payment required.

- After receiving your order, we will contact you and share you with discount according to the quantity.

- If you confirm the order, you can proceed the payment when order is updated with price adjustment.